I put my previous project on hold recently, as I wanted to create a better way of logging system status in my embedded projects. Luckily for me, the people who make vcdMaker already had a great way to do this. In the video below, I got a bit more into detail about how I log the information. Please visit the vcdMaker website and check out the videos, they are really good. I hope that you find vcdMaker as useful as I do.

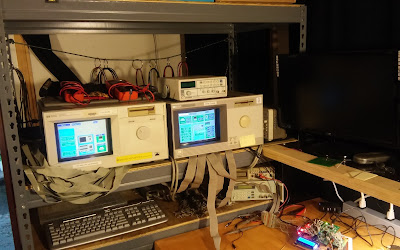

The log output is only as good as it's time stamp, so I wanted to ensure that my time stamp was good. I usually run my SysTick handler at 1 kHz or 1 ms tick rate. I enabled a general purpose input / output pin on the STM32F429 micro controller and had it toggle on and off. I was able to verify with the Logic Analyzer and the Scope that the tick rate is indeed 1 kHz. You can see those screen captures below.

|

| Logic Analyzer screen capture |

|

| Oscilloscope screen capture |

My system clock and advanced high performance bus clocks are setup as 180 MHz. The advanced peripheral bus 1 clock is set to 45 MHz, while the advanced peripheral bus 2 clock is set to 90 MHz.

This allows me to set USART 1 to 115200 baud, for now this is adequate. I may need to speed this up in the future. The USART Driver is called from the _write() system call, which allows me to use stdio printf function to print the messages to the USART.

I created a little API to log messages:

log_signal_message(char* signalname, uint8_t signal_size, char* format, ...)

log_signal_event_message(char* signalname, char* format, ...)

log_message(eMessageType_t type, char* format, ...)

The messages logged by these functions are queued for the logger task to print to the USART. The logger task is only 1 priority level higher than the idle task. This allows the logger task to send messages without interfering with tasks that have higher priority. The logger task uses a blocking call to receive from the queue, with a delay set to the maximum available. The allows the task to only work when it must. The video below gives some more information as well as a short demo of how I am using this setup. Hopefully, you find this useful.